����FPGA�����l�x�����OӋ

�c�������õ��Ԅ��R�e���g��l�δa�ʹŗlһ�ӣ��o�����l�R�e��RFID" target="_blank">RFID�����gҲ��һ�N�Ԅ��R�e���g��ÿһ��Ŀ�ˌ��������l�x�����Ќ���Ψһ������R�e�a��UID��������“��Ә˺�”���˺����������w�Ϙ��RĿ�ˌ����缈�䡢؛�P����b��ȡ����l�x������������������Ә˺����xȡ�R�e�a��

������RFIDϵ�y�������ֽM�ɣ��쾀��Ȧ����RFID��a�����հl����RFID��Ә˺���ÿ���˺�����Ψһ������R�e�a������1�@ʾ�˳��õ��Ă�RFID�l�ʼ��䝓�ڵđ����I�����У�Ŀǰ�̘I�ϑ����^�V���dz����l��UHF�������ڹ���朹������п��ܵõ��V���đ��á�

EPC��Ә˺�

EPC��ʾ��ӮaƷ���a����RFID��Ә˺��Ę˜ʣ���������Ә˺��Ĕ������ݺ͟o��ͨ�Ņf�h��EPC�˜ʌ��l�δaҎ���еĔ�����Ϣ�˜��cANSI�������˜ʻ��M����802.11b���ƶ��ğo������ͨ�Ř˜ʽY����һ��Ŀǰ�����ڹ���朹����е�EPC�˜ʣ����ڵڶ���EPC Class-1�˜ʡ�

Class-1�˺��ڳ��S�r�ѽ������룬��Ҳ�ǿ��ԬF�����d��ͨ����r�£�һ���˺��ѱ����룬�ȴ漴���i�������ٴΌ�����Ϣ��Class-1�˺����ó�Ҏ�ķֽM��ݔ�f�h—�x�����l�Ͱ������P����͔����Ĕ��������˺��S������푑���

���ӵ��x�������íh��

RFID�đ��íh�����ܷdz����ӡ��ŵ��Ĺ����l�������S�ɵĹ��I���Ƽ��c�tˎ��ISM���l�������l���е�RFID�x�����ܵ����ԟo�K�Ԓ���o���������o�������W�j�Լ������R���x�����ĸɔ_����회�ÿһ�x������RF������ǰ���OӋ���܉�������ɔ_��̖������a���Ɍ���ԃ���e�`��ʧ�档������������횱������^�͵�ˮƽ���Ա�߂����ĄӑB�������Ķ��ԟo�e��ʽ�z�y�����ƽ�˺�푑���̖��

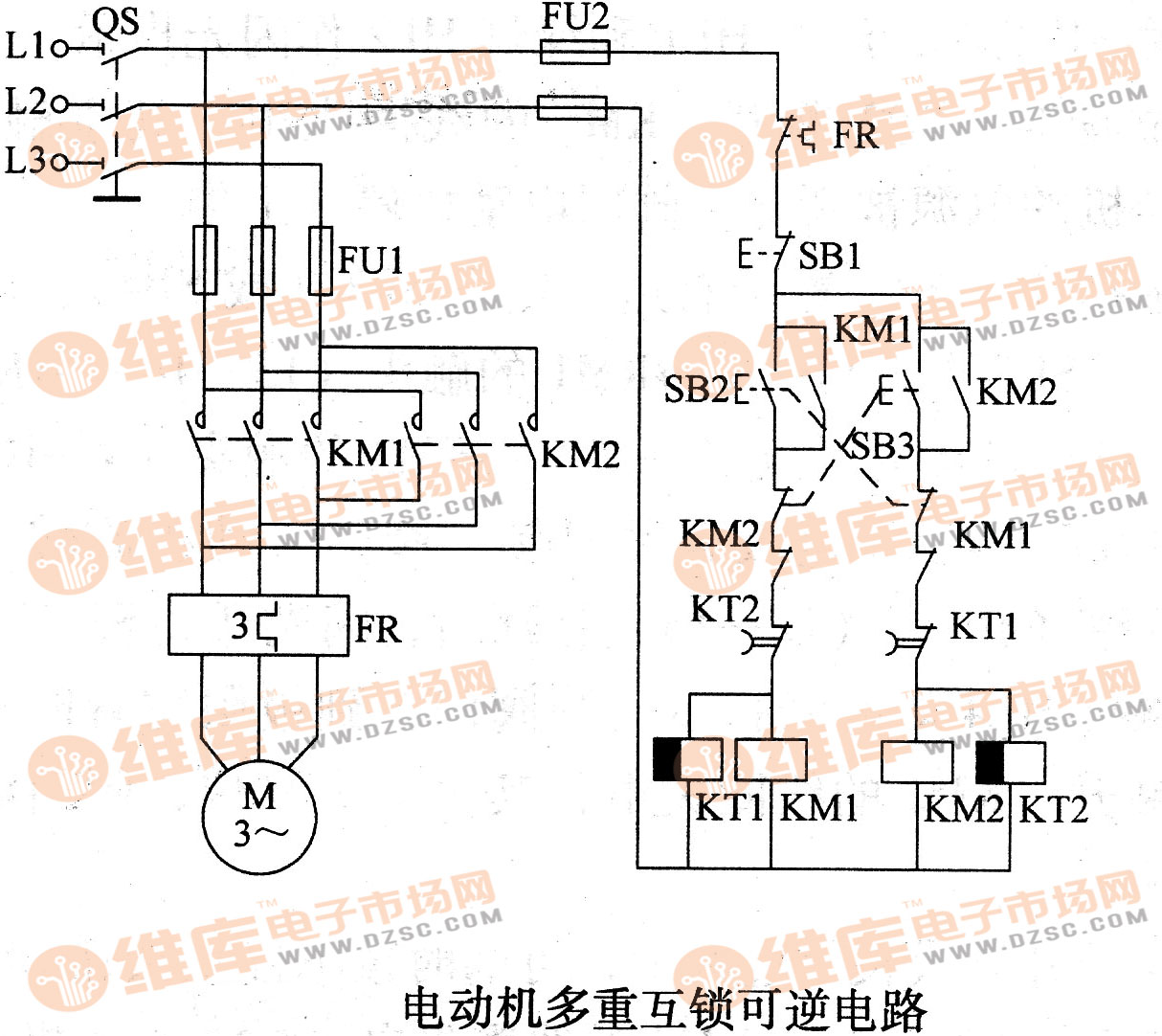

�D1����ʾ���x����RF���l�հl������һ��������OӋ���܉��ڴ��ڴ����ɔ_Դ�Đ��ӭh���з����ع������l�����ͽ�����������һ���߄ӑB����ֱ���D�Q�{�����ͽ��{��������^���ȵ�����˷����Բ������˳ɱ���

���úͿɿ������l�������OӋ

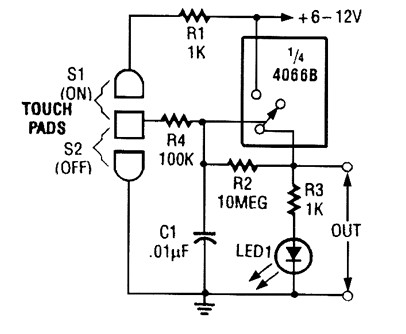

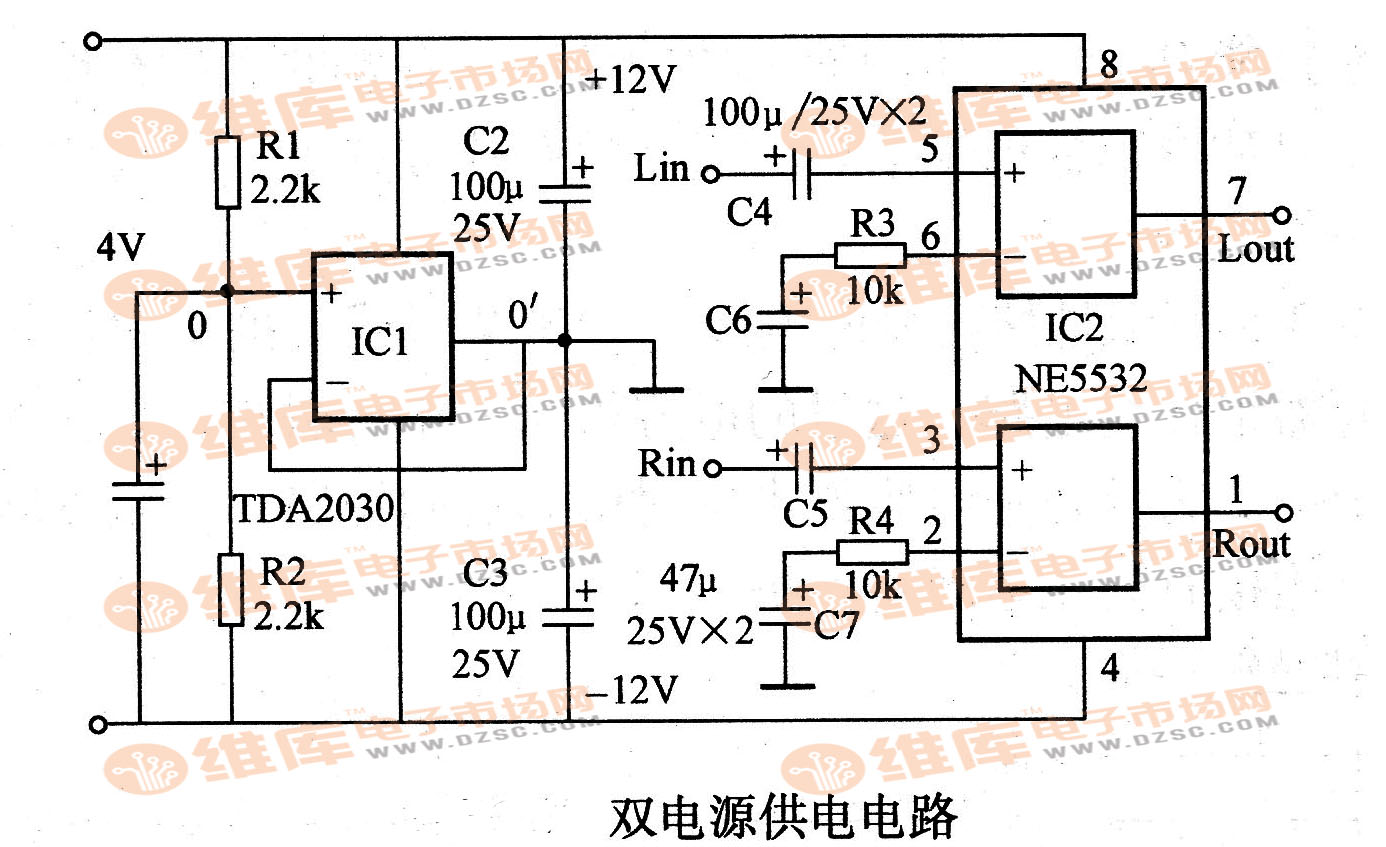

�������ĺ�����Linear��˾��LT5516���@��һ�N�߶ȼ��ɻ���ֱ���D�Q�������{����оƬ���ṩ��һ�����_������������0����90�ȣ��������쾀����̖��ͨ�^���l�V����֮��ͨ�^һ����ƽ��׃����ֱ��ݔ�뵽���{��ݔ��˿ڡ�����LT5516����ϵ���ܵͣ��ڲ���Ҫ����Ŵ�����LNA������r�£����ܱ�����21.5dBm IIP3��9.7dB P1dB�����ܡ�

�ڽ��Ք����r���x�����l���B�m�d����δ�{�ƣ����Ա��˺��ṩ�Դ�����յ�Ո�����Ә˺�ͨ�^���d���M���{����푑�һ���a���������õ��{�Ʒ�ʽ������I�أ�ASK�����߷���-�����I���I�أ�PR-ASK�������{�����Ѓɂ����������z��ʽݔ���˿ڣ���˾߂���Ȼ�ķּ����չ��ܡ�������ڶ�·����λȡ������ij��ͨ���o��������̖����һ�lͨ��������90�ȣ��Ϳɽ����^������̖����֮��Ȼ���@�ӣ����w���տɿ��Ծ͵�����ߡ�

һ�����{��ɣ����Ɍ�I�����ȣ���Q��������λ�����ݔ����̖��AC��ʽ�����һ���\��Ŵ����������Þ�һ����ַŴ��������S���D�Q��ζ�ݔ����̖���@���r����ͨ���l���O�Þ�5KHz�����ڽ��Ք��������^С��̖�l�ʣ������^��������l�ʣ����ܱ��\�Ә˺����ã���ͬ�r���ָ���������l�ʣ�60Hz�����@�ӣ�ݔ����̖�������ñ����Þ����A��ͨ��LT1568������^��ͨ�V��������ͨ���l�ʑ����O�Þ�5MHz���Ա��^��a����̖���^�V�������_��������

������̖Ȼ��һ���p·����ģ���D�Q����LTC2291���ֱ��ʞ�12λ���M�Д��ֻ�̎�������ژ˺��a���Ď�����5KHz��5MHz��LTC2291�܉���25MSps�������M�г�ֵIJɘӣ��Ķ����_�ز��@���{��̖������Ҫ�ĕr��߀���ڻ���DSP�Ќ��F�~��Ĕ��֞V�����@�ӣ����������ܾ߂��^���߉�ֵ�O���`���ԣ�ԓ�O�ÿ��ɻ���̎�����Ԕ��ֻ���ʽ���С�

�����΄պ͔��ֻ����l�ŵ���̎�����������ȫFPGA��Q�������F���������ͼ��ɶ�

�߄ӑB�������l�l�����OӋ

�l����������һ���R������ֱ���D�Qʽ�{������LT5568�߂�ܸߵľ��ԶȺ��^�͵ı�����������܉�����l�����̖�ṩ��ɫ�ĄӑB�������ܡ��{�����܉�Ĕ�ģ�D�Q����ACPR���������ڝM��l���l������Ҫ�����磬���{�������lݔ���ƽ��-8dBm�r��ACPRָ�˃���-60dBc�����ھ߂����ɫ��ACPR���ܣ���̖�ɱ��Ŵ����S�ɵ�1w���ʣ���������+30dBm�������߷Ŵ���2w���Է��ϚW��Ҏ�����������ɷN��r�£���Ҫ���DZ����ƽ�̶������ԓ�ƽ��������Ә˺��ṩ�Դ�����^���x�����x��LTC5505�����l���ʙz�y���ăȲ��ض��a�����ܣ��ɜʴ_�y�����ʣ��ṩ�����ķ�����̖�����{�����l���ʷŴ�����ݔ�����ʡ�

����̎���;W�j�ӿ�

�ڻ����l���ϣ�FPGA���аl����DAC�́���ģ���D�Q����ADC���IJ��ε��ŵ����΄ա��@һ�^��Ҳ���Q�锵�����l

̎�����漰�V����������ơ��l���D�Q�Ͳɘ���׃���ȡ�FPGA�������Բ���̎�������ŵ���

�D2�@ʾ��һ�����l�x�����ļܘ�����������̎���΄հ�����

- �Ȍ��ֶΙz�y

- �����Ӌ

- �{�ƺͽ��{��ASK���l���I�غ������I�أ�

- ��̖�a��

- ���P��̎��

- ��ֵ�z�y���ֵ�O��

- CRC�m�e����

- ���a�ͽ�a��NRZ��Manchester���ΘO�ԡ�����p�O�Ժ�Miller��

- ���z�y

- IDȥ�_

- ��ȫ��������

���յ���RFID�˺�������ͨ�^���ڻ�W�j�ӿڱ���������Iϵ�y���������@�N���y�ļܘ�������׃��һ�����ֲ�ʽ TCP/IP �W�j��һ�����֡���ԓ�W�j�У����l�x������ؓ؟�����R���Ę˺���

���@�N��r�£����l�x������������Ә˺����B������Iܛ��ϵ�y���ǻ��ֲ�ʽ������֮�g�ľW�P��

ȡ�Q��Ӳ��/ܛ�����ܷօ^��r���@Щ�����΄ռ�����FPGA����ɣ�Ҳ����DSP����ɣ������ɶ����ֈ��С�Xilinx��˾�Ƴ���һ��IP�Ⱥ��������а���FIR��CIC��DDS��DUC��DDC���������P��������/����LUT�ȡ��@Щ߉�·�dz��m�ψ��м��������΄գ��������������λ�Ĵ�����XOR����ᘌ�Xilinx® VirtexTM-4ϵ�е�DSP48����ʮ���m�ψ���������̖̎���΄ա�

һ������̎����ؓ؟���Ƹ��N����̎���΄յĹ����Ժ��{�ȣ�߀ؓ؟�·�Ӆf�h���@Щ����̎���΄հ������l���l��ǰ�� �����_ͻ�㷨̎���ȡ�����̎����߀�ṩ����̫�W��USB���̼��Ƚӿڡ�

�����΄պ͔��ֻ����l�ŵ���̎���������ȫFPGA��Q�������������ͼ��ɶȡ�FGPA���ܡ�DSP���ܣ��Լ�����̎�����ܣ����ɱ�������һ������Ƕ��ʽ̎������FPGA��

�D 3 �@ʾ��һ������ FPGA �� RFID ̎�����ļܘ���Ƕ��ʽ̎����������һ��Ӳ�ˣ�Ʃ�磬Virtex-4 FX�aƷ������õ�PowerPCTM����߀������һ��ܛ�� ��Ʃ��SpartanTM�O���в��õ�MicroBlazeTM����������PowerPC��MicroBlaze�ĽY���w���Ñ����Ԍ�����Ӳ��̫�WMAC��EMAC���B�����ⲿ��̫�W����ӣ��M���B������̫�W�����⣬�Ñ�߀��ʹ������10/100-BaseT��Lite Ethernet MAC IP��

PowerPC/MicroBlazeǶ��ʽ̎�������������΄գ�

- EPC����̎����ǰ�D

- �f�h̎��

- ԃ���{��

- TCP/IP �W�j�ӿ�

- ���ƺͱOҕ

- �{�ƽ��{������

- ��������

- HTTP������

- SNMP/MIB̎��

Xilinxǧ����̫�Wϵ �y �� �� �O Ӌ��GSRD����һ������EDK�ą���ϵ�y���܉��ڻ���TCP/IP�ąf�h�ӿں��Ñ������ӿ�֮�g����һ�������ܵĘ�����GSRD�ĽM���߂�M��TCP/IPϵ�yÿ���غ�ÿ���_�NҪ��Ĺ��ܡ�

Xilinx߀ᘌ�Monta Vista Linux �� Treck�ї��ṩ�˰l�����ܻ��ʡ����� Xilinx Platform Studio ��XPS��̎�����춨�x��Nucleus PLUS RTOS�������MicroBlaze��PowerPC̎������ϵ�y�������µă��ݡ�Nucleus PLUS RTOS�ߴ��С���@��ζ�����܉�����Ƭ�ϬF�еĴ惦�����Ķ��^���Ƚ����ģ�������ܡ����⣬�V�������g��ʹ��Nucleus PLUS RTOS�ɞ�RFID��˾W�j����

���P��x:

- ...2011/12/02 16:57������FPGAֱ�����ДU�lϵ�y���OӋ

- ...2011/11/07 15:11������FPGA�ĸ��ٴ��Ђ�ݔϵ�y���OӋ�c���F

- ...2011/11/07 15:10������FPGA��ͨ�î����հl���OӋ

- ...2011/11/07 15:10������FPGA���h���x�y��������ϵ�y�OӋ

- ...2011/10/31 16:02������FPGA�Ĕ����ɼ�ϵ�y�OӋ

- ...2011/10/31 16:02������FPGA�Ľ�ͨ��ϵ�y�����OӋ

- ...���D��Ԕ����܇�x���屳���܇Ҏ����ȫ�OӋҪ��

- ...��ʹ���а�ȫ���ϵ��W��惦������ȫ����܇ϵ�y

- ...������ƫ�ò�־��Ԃ��������^���Mչ�͑���

- ...�����¿�˹�y�uijƷ�����ܲ����������C����ƪ

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�(�m)

- ...���������ʽ�ضșz�y���y��ϵ�y�Є�����ʧ���Ӱ�

- ...��RTD�y��ϵ�y�Є�����ʧ���Ӱ�

- ...���{��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^�e

- ...�� ��о�������ø�Уδ����܇�˙C�����OӋ��ِ������ʽ����

- ...�� ̽�صڶ����l�{ɽ�������¡�������ԇ�gՓ����

- ...�� ��2018�Ї��댧�w���B朴�����ڽ��Kʡ�����e��

- ...�� �����}��Ҏ����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�������ܵ�����

- ...�� �ⷨ�댧�w��ST����Cinemo��Valens��CES 2018չ������ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a�I���°lչ�߷�Փ�������ھ����_

- ...�� ����늙C���ݳ���PCIM����2017չ

- ...�� GPGPU���a������Ї�оƬ�a�I�Ŀհ؎�

- ...�� ���W�aƷ�OӋ��Wi-Fi�B�ӵ��Ă��P�I����

- ...�� �������Ї�MEMS���܂������a�I�lչ��������ڰ������_�Ļ

- ...�� IAIC���ِ���[���Ї�о�����Ä��£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �yԇ���g

- ...�� �����Ј��������L�Ƅ�Molex�ӏ���܇�I��İlչ

- ...�� �Ї��Gɫ�����˳���������_�ڼ� ���a�W���ù�̽�Gɫ�lչ��ģʽ

- ...�� Efinix® ȫ����AI߅��Ӌ�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r���aƷ�Uչ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M���������I�ǻ�������

- ...�� ��늮aƷ�_�l���yԇ��ӑ����������Դ�����ɹ��e��

- ...�� Manz���ǿƼ�����댧�w�I�� ����弉�ȳ��ͷ��b�ṩ���W���Ƴ̡�Ϳ�������⑪�õ����a�O���Q����

- ...�� ������ABITRODE����늳yԇϵ�y���������������Դ

- ...�� ������AFTFϵ��늳yԇϵ�y�И˱�������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ�dϵ�y�ɹ����������؈

- ...�� ������A���H��늄���܇���P�I�����y�u��ӑ�������[���M�y�u���g

- ...�� �����ɼ��K��ϵ�y�O��

- ...�� ���x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|�J�C����܇ϵ�ЮaƷӋ��

- ...�� ���`˼® �����U������� ⁽�ϵ��™ FPGA �aƷ ⁽�ϵ�ЮaƷ�U�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_�e� (TSMC) 16�{��ˇ���c��Ƭ

- ...�� TI��2019��ȫ����W������OӋ��ِ�C����Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C�@��ȫ���ׂ���܇��ȫ�����Եȼ�(ASIL) ��D���J�C

- ...�� ���R��܇�x��BlackBerry������һ����܇