FPGA�c��Ƭ�C(j��)��(sh��)�F(xi��n)���l��(sh��)��ʽ��λ�y(c��)��?j��)x

ժҪ���������AVR ATmega128��Ƭ�C(j��)��Altera��˾��Cycloneϵ��EP1C3T100����ĵ�ϵ�y(t��ng)�O(sh��)Ӌ(j��)�����������˔�(sh��)��ʽ���l��λ�y(c��)��?j��)x�Ĝy(c��)��ԭ���͜y(c��)���`��������ķ�������Ҫ��B��ϵ�y(t��ng)��ܛӲ���O(sh��)Ӌ(j��)����(sh��)�`�������˷����O(sh��)Ӌ(j��)����λ�x��(du��)���l���Ҳ���̖(h��o)��(sh��)�F(xi��n)���_�y(c��)�l�͜y(c��)��λ�����̎���ٶȿ졢��(w��n)���ɿ������ȸߵȃ�(y��u)�c(di��n)��

�����P(gu��n)�I�~����(sh��)����λ�x;��Ƭ�C(j��);FPGA;�`��;�l��;��λ��

�������O(sh��)Ӌ(j��)����MCU��FPGA��Y(ji��)�ϵ�ϵ�y(t��ng)��������AVR��Ƭ�C(j��)ATmega128��Altera��˾��Cycloneϵ��EP1C3T100����ģ���ְl(f��)�]���Եă�(y��u)��(sh��)����AVR��Ƭ�C(j��)���M(j��n)��RISC�Y(ji��)��(g��u)�͏�(qi��ng)�ŵ��\(y��n)�㡢���ƹ��ܣ�Altera��˾��FPGA�\(y��n)���ٶȿ졢�YԴ�S���Լ����̵����c(di��n)�������O(sh��)Ӌ(j��)���˷�������λ�x�߂��ٶȿ졢��(w��n)���ɿ������ȸߵȃ�(y��u)�c(di��n)����������(sh��)�F(xi��n)“���ܻ�”��“�Ԅ�(d��ng)��”��

����1 ϵ�y(t��ng)�����O(sh��)Ӌ(j��)

����1.1 �y(c��)�������ı��^�c�x��

����Ŀǰ��λ�y(c��)���ķ�����Ҫ�ЃɷN��

����1)DFT�y(c��)�෨�������y(c��)��̖(h��o)ͨ�^A/D�D(zhu��n)�Q�õ�f(n)��f(n)���xɢ�����~׃�Q�ó��xɢ�l�VF(k)��f(n)��F(k)�鸵���~׃�Q��(du��)��ͨ�^�\(y��n)��õ���·��̖(h��o)�Ļ�����λ���Ķ�Ӌ(j��)�����λ�DFT�y(c��)�෨�ľ���������ADC�IJɘӾ��ȣ���Ҫ����ADC��(du��)��̖(h��o)�M(j��n)���^�ɘӣ��y(c��)��������(f��)�s������ͨ�^�ɼ�����Ӌ(j��)��C(j��)�ό�(sh��)�F(xi��n)̓�M�x����������Ҫ��(y��ng)���ھ���Ҫ��ܸߵĈ�(ch��ng)�Ϻ�̓�M�x���С�

����2)���Ӌ(j��)��(sh��)�y(c��)�෨ ����·ͬ�l��������̖(h��o)��(j��ng)�^��̖(h��o)�����·��õ�������̖(h��o)��������̖(h��o)��(j��ng)�^�b�����õ���·ݔ����̖(h��o)����λ����̖(h��o)���ù̶��l�ʵIJɘ��}�_�M(j��n)����䲢Ӌ(j��)��(sh��)���Ķ�Ӌ(j��)�����λ����Ӌ(j��)��(sh��)�y(c��)�෨��Ҫ��(y��ng)����Ҫ��һ���ľ��ȣ��y(c��)�����l�ʲ���̫�ߵ���(sh��)�r(sh��)��Ҫ���(qi��ng)�Ĉ�(ch��ng)�ϣ����ڌ�(sh��)�F(xi��n)��(sh��)�ֻ����Ԅ�(d��ng)�������l��(sh��)����λ�x�m�������Ӌ(j��)��(sh��)����

�������Ӌ(j��)��(sh��)�y(c��)�෨�Ļ����㷨�������Ҳ����κ�ķ�����̖(h��o)�l�ʞ�f�����ڞ�T���ɘ��}�_���ڞ�TC������һ��(g��)���ڃ�(n��i)��(du��)�ɘ��}�_Ӌ(j��)��(sh��)�飬n�t���y(c��)��̖(h��o)�l��f=1/T=1/nTC��ͬ�ӵķ����y(c��)���ɂ�(g��)ͬ�l���Ҳ����c(di��n)֮�g�ĕr(sh��)�g����t���t����̖(h��o)����λ���θ=��t·360°/T��

����1.2 ϵ�y(t��ng)�����Ĵ_��

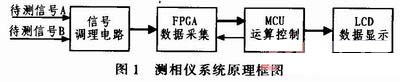

������ϵ�y(t��ng)�y(c��)��������֪����(sh��)��(j��)��Ҫ�ɼ����\(y��n)�㼰�@ʾ�����]��Field Programmable Gate Array(FPGA)���ɶȸߡ�I/O�YԴ�S������(w��n)���ɿ����x����ش����Ԫ�����٣������r(ji��)���½��ȃ�(y��u)��(sh��)���Լ�MCU���õ��˙C(j��)�ӿں��\(y��n)����ƹ��ܣ����Ա�ϵ�y(t��ng)��MCU��FPGA��Y(ji��)�Ϙ�(g��u)�ɜy(c��)�����w��FPGAؓ(f��)؟(z��)�ɼ��y(c��)�l�͜y(c��)��λ����}�_��̖(h��o)��MCUؓ(f��)؟(z��)�xFPGA�ɼ��Ĕ�(sh��)��(j��)��Ӌ(j��)����y(c��)��̖(h��o)�l�ʺ���λ���LCD���@ʾ��

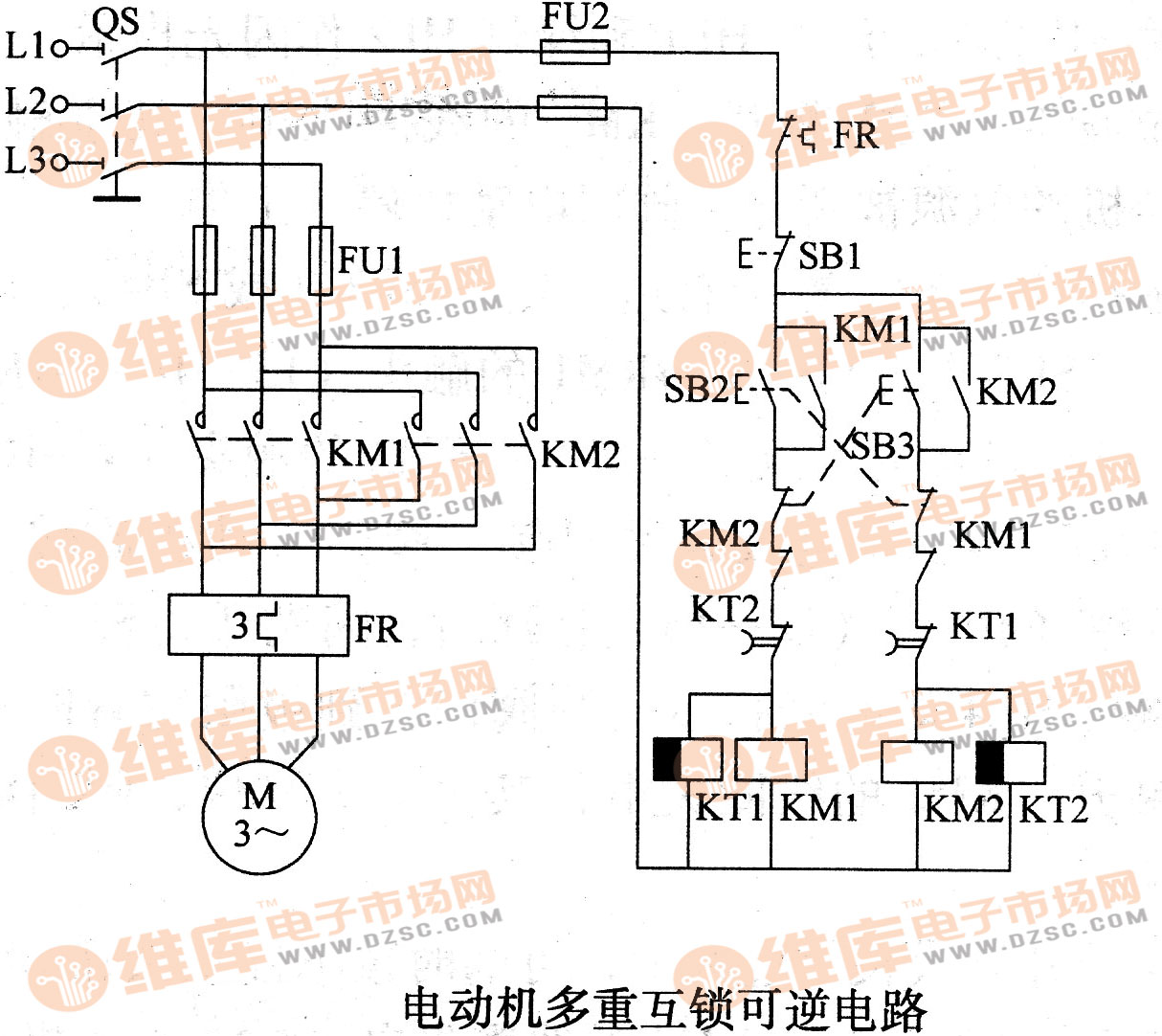

�������ԣ�ϵ�y(t��ng)��4��(g��)���ֽM�ɣ����y(c��)��̖(h��o)�{(di��o)���·��FPGA��(sh��)��(j��)�ɼ��·��MCU��(sh��)��(j��)�\(y��n)������·��LCD��(sh��)��(j��)�@ʾ�·����D1��ʾ��

����2 �y(c��)���`��ķ����c����

������λ�y(c��)��?j��)x�������O(sh��)Ӌ(j��)�����HҪ�к��m�Ĝy(c��)��������ϵ�y(t��ng)��(sh��)�F(xi��n)������߀��Ҫ���ط����`��a(ch��n)����ԭ��ʹ_�������ķ�����

����1)���r(sh��)��l��(����(sh��)��(j��)�ɘ���̖(h��o))��Ӱ��c�_������λ�y(c��)��?j��)x�Ĝy(c��)�l������20 Hz��20 kHz����λ��ķ������θ=0°��359.9°����λ����@ʾ�ֱ��ʞ�0.1°��Ҫ��y(c��)����λ�Ľ^��(du��)�`��≤2��

�������y(c��)�l��20 Hz≤f≤20 kHz���t����50μs≤T≤50 ms��

����T=50 μs���^��(du��)�`��ȡ0.1°��2°��

�����t���r(sh��)���̖(h��o)���ڣ�0.1°x50 μs/360°≤TC≤2°x50 μs/360°����1/72(μs)≤TC≤1/3.6(μs)�����Եó����r(sh��)��l�ʣ�

����3.6 MHz≤fC≤72 MHz��

����T=50ms��(n��i)��(du��)TC=1/3.6(μs)������}�_Ӌ(j��)��(sh��)��Ӌ(j��)��(sh��)ֵNmin=180000≤218;��(du��)TC=1/72(μs)������}�_Ӌ(j��)��(sh��)��Ӌ(j��)��(sh��)ֵNmax=3600000≤ 222��

�������O(sh��)Ӌ(j��)���]MCU��Ӌ(j��)�㼰���lȡ����̖(h��o)�ķ��㣬���r(sh��)���̖(h��o)�l��fC=20 MHz���y(c��)���^��(du��)�`��<1°��F(xi��n)PGA��20 MHz�r(sh��)���̖(h��o)������(du��)���y(c��)��̖(h��o)���ں���λ��(du��)��(y��ng)�ĕr(sh��)�g���M(j��n)��Ӌ(j��)��(sh��)��F(xi��n)PGA�ɘӵĶ��M(j��n)�Ɣ�(sh��)��(j��)λ��20 bit�����Ա��C�y(c��)���ľ��ȡ�

����2)���y(c��)��̖(h��o)�{(di��o)���·�����c(di��n)Ư�Ƶ�Ӱ��c�������y(c��)��̖(h��o)�{(di��o)���·��Ҫ�����ǰ�ݔ����̖(h��o)����׃�Q�ɾ��β���ͨ�������^����^������ʩ�����|�l(f��)����

�����^����^�������c(di��n)�λ�������ܕ�(hu��)����ʎ��ݔ����̖(h��o)�����c(di��n)�λ�����r(sh��)��늉����^��̎�ڷŴ�^(q��)�����κ�ľ��β���߅�ؕ�(hu��)�a(ch��n)������(d��ng)��ʹϵ�y(t��ng)�o���M(j��n)�Мy(c��)����Ҫ�����@�N����(d��ng)�����Բ���ʩ�����|�l(f��)�������˱��C�y(c��)���ľ��ȣ�ʩ�����|�l(f��)����횷��σɂ�(g��)�l����һ�ǃ�·���y(c��)��̖(h��o)���Ȼ�����ȣ������T���ƽҪ�����ӽ���

����3)���κ�߅�صĶ��ͳ̶ȵ�Ӱ��c������̖(h��o)��(j��ng)�^���κ�ݔ���ľ����}�_��̖(h��o)ֱ���ͽoFPGA���tFPGA���������@ȡ��(w��n)���Ĕ�(sh��)���}�_��̖(h��o)���͕�(hu��)ʹϵ�y(t��ng)�ľ����ܵ��ܴ�Ӱ푡��@��Ҫ���������κ�߅�ز�������ɵġ�Ҫ��Q�ˆ��}��һ���xȡ�����^�[�ʵ������������ڱ��^���ĺ�˼�һ��(j��)���·�������}�_��̖(h��o)��߅�ء�

����4)�е��l�y(c��)�����ȵ�Ӱ��c��������20 MHz��(sh��)��(j��)�ɘ���̖(h��o)��ѭ�h(hu��n)Ӌ(j��)��(sh��)���y(c��)��̖(h��o)�����ڼ���λ�(du��)��(y��ng)�ĕr(sh��)�g������_(d��)��0.05 μs��20λ��(sh��)�����Ć�λ��0.05μs�����ñ��y(c��)��̖(h��o)ˢ�²ɘ�Ӌ(j��)��(sh��)����(sh��)�F(xi��n)���l���y(c��)�������l�ٜy(c��)�����r(sh��)�gӋ(j��)��(sh��)���_�ɿ����@�ӣ�F(xi��n)PGA���Ԟ�MCU�ṩ��(w��n)���Ĕ�(sh��)��(j��)��

����3 ϵ�y(t��ng)Ӳ���·���O(sh��)Ӌ(j��)

����3.1 ǰ����̖(h��o)�{(di��o)���·���O(sh��)Ӌ(j��)

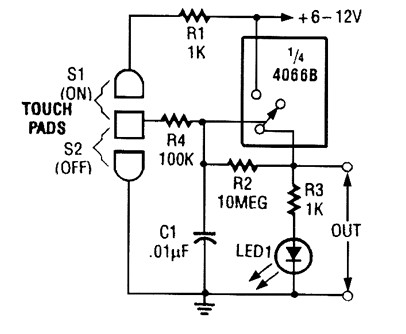

����ʩ�����|�l(f��)��(�t�����^��)�mȻ���Ժܺõ��������^���^������Ķ���(d��ng)��������ݔ����̖(h��o)��ݔ����̖(h��o)������λ������·���y(c��)��̖(h��o)�ķ��Ȼ�������҃ɂ�(g��)ʩ�����|�l(f��)�����T���ƽ�ֺܽӽ����tʩ�����|�l(f��)���������λ�`�(du��)�y(c��)��ϵ�y(t��ng)�`����oӰ푡�

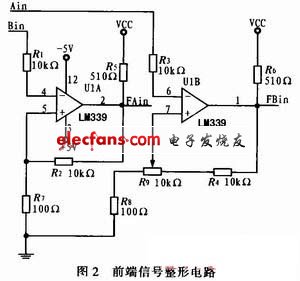

��������LM339��(n��i)����4��(g��)��(d��)����늉����^����ԓ늉����^�������c(di��n)�ǣ�ʧ�{(di��o)늉�С������ֵ��2 mV;�Դ늉����������p�Դ늉���±1��±18 V;��(du��)���^��̖(h��o)Դ�ă�(n��i)�������^����ͬ��ͷ���ݔ���늉���e����10 mV���ܴ_��ݔ����һ�N��B(t��i)�ɿ����D(zhu��n)�Q����һ�N��B(t��i)��ݔ�����ஔ(d��ng)��һֻ���Ӽ�늘O���ľ��w���O�ܣ���ʹ�Õr(sh��)ݔ���˵����Դһ��횽�һֻ��衣����׃늉�ֵ�����ĸɔ_�����^�ز�A(y��)U��ݔ��늉���ֵ�͌��Ƿ�(w��n)���ġ����������Լӿ���^����푑�(y��ng)�ٶȡ������t�����^���ӵ���������(qi��ng)���h(yu��n)���·�еļ�����Ϗ�(qi��ng)�ö࣬���Կ���������·������϶��a(ch��n)�����Լ���ʎ��ͨ�^�{(di��o)��(ji��)�λ����ʹ�ɂ�(g��)ʩ�����|�l(f��)�����T���ƽ������ȣ����Cݔ���·��(du��)��λ��y(c��)���������`��·��D2��ʾ��

����3.2 ϵ�y(t��ng)�y(c��)���·�O(sh��)Ӌ(j��)

�����Ԇ�Ƭ�C(j��)������O(sh��)Ӌ(j��)��λ�x�����侧���24 MHz����Ƭ�C(j��)C/T��Ӌ(j��)��(sh��)�`���1��(g��)�C(j��)�����ڞ�±0.5 μs���t�^��(du��)�`���360°x0.5 μs/50μs=3.6°�����ԣ���(d��ng)���y(c��)��̖(h��o)�l�ʺܸߕr(sh��)���y�M��y(c��)��Ҫ��

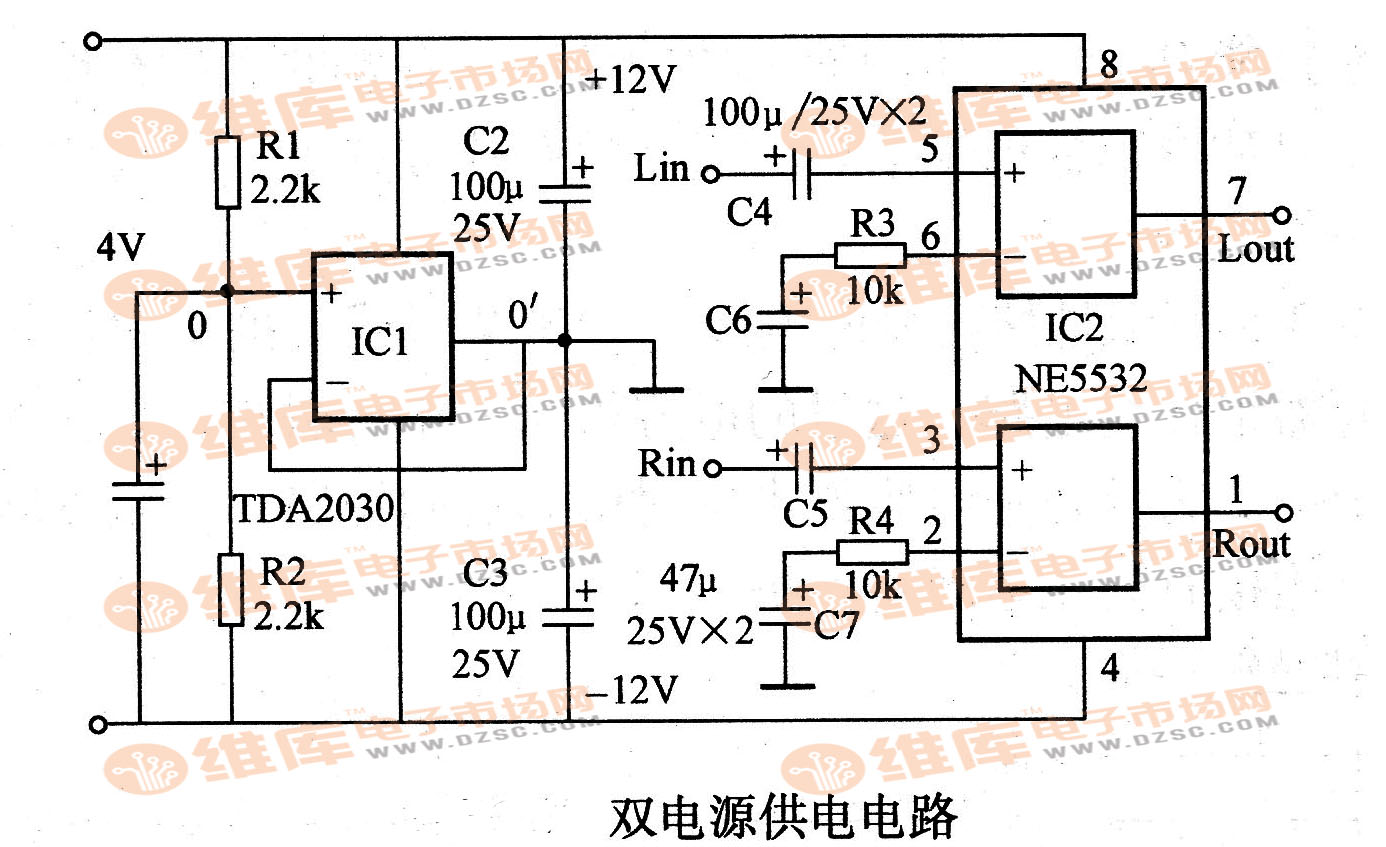

�������O(sh��)Ӌ(j��)����AVR��Ƭ�C(j��)�cFPGA��Y(ji��)�ϵķ�����F(xi��n)PGA��(sh��)�F(xi��n)��(sh��)��(j��)�ɼ��������y(c��)��̖(h��o)���l�ʺ���λ������(du��)��(y��ng)�r(sh��)�g���D(zhu��n)�Q����M(j��n)�Ɣ�(sh��)��(j��)���o��Ƭ�C(j��);��Ƭ�C(j��)��FPGA�@ȡ��(sh��)��(j��)����(j��ng)�^�\(y��n)�㡢�D(zhu��n)�Q�Ȕ�(sh��)��(j��)̎���������y(c��)��̖(h��o)���l�ʺ���λ����LCD���@ʾ��

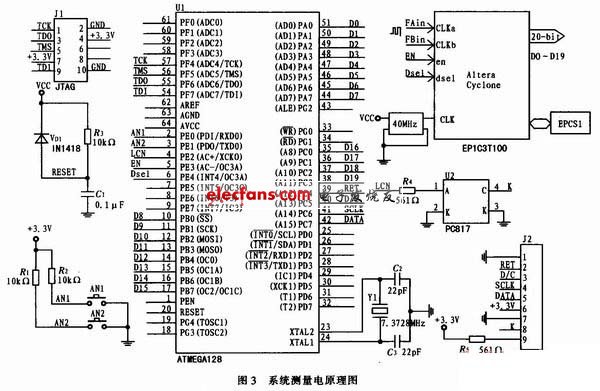

��ϵ�y(t��ng)�ԭ��D��D3��ʾ��MCU����ATMEL��˾��AVR��Ƭ�C(j��)ATmega128���������M(j��n)��RISC�Y(ji��)��(g��u)�������(sh��)ָ����һ��(g��)�r(sh��)����ڃ�(n��i)��ɣ���32��(g��)8λͨ�ù����Ĵ��������O(sh��)���ƼĴ������˷���һ���Ƭ�C(j��)��һ�ۼ�����(sh��)��(j��)̎�펧����ƿ�i����128 KB��ϵ�y(t��ng)��(n��i)�ɾ���Flash��4 KB��EEPROM�Լ�4 KB�ă�(n��i)��SRAM����ѭJTAG��(bi��o)��(zh��n)��߅����蹦�ܣ�֧��?j��n)Uչ��Ƭ��(n��i)�{(di��o)ԇ����ͨ�^JTAG�ӿڌ�(sh��)�F(xi��n)��(du��)Flash��EEPROM���۽zλ���i��λ�ľ��̡�

����FPGA����Altem Cycloneϵ�е�EP1C3T100������оƬ��EPCS1��VHDL���ܳ���(j��ng)�^ȫ���g��(hu��)����.sof��.pof�ļ������õ����d��Byte-Blaster II��[Mode]�(xi��ng)�x��“JTAG”���.sof�ļ����õ�FPGAоƬEP1C3T100�У������{(di��o)ԇ;[Mode]�(xi��ng)�x��“Active Serial Programming”���.pof�ļ����d������оƬEPCS1�У�ϵ�y(t��ng)������늕r(sh��)�����\(y��n)�С�

����LCD����HTM12864����128x64���Д�(sh��)��(j��)����Һ���@ʾ���������ͨ�^�����ܵ����ơ�

����ATmega128��EP1C3T100�O(sh��)Ӌ(j��)���Ե�JTAG�ӿڡ��D3�L����ATmega128��EP1C3T100�Ľӿ�D0��D19��EN��Dsel��LCN;ATmega128�cHTM12864�Ľӿ�RET��D/C��SCLK��DATA;EP1C3T100��ݔ����̖(h��o)FAin��FBin��66 MHz�ⲿ��Դ��������оƬEPCS1��4 ϵ�y(t��ng)ܛ�����O(sh��)Ӌ(j��)

����4.1 FPGA��(sh��)��(j��)�ɼ�VHDL�����O(sh��)Ӌ(j��)

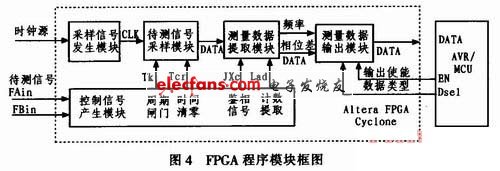

����FPGA��(sh��)��(j��)�ɼ���VHDL�����O(sh��)Ӌ(j��)����Altera QuartuslI�_�l(f��)ܛ��ƽ�_(t��i)����(sh��)�(y��n)�_�l(f��)ϵ�y(t��ng)����ɵġ������O(sh��)Ӌ(j��)�����������(up-to-down)���O(sh��)Ӌ(j��)������FPGAϵ�y(t��ng)��ģ�K��(g��u)����D4��ʾ���ɘ���̖(h��o)�l(f��)��ģ�K��ɕr(sh��)���̖(h��o)Դ�ķ��l�������õ�CLK=20 MHz;���y(c��)��̖(h��o)�ɘ�ģ�K�ڿ�����̖(h��o)�a(ch��n)��ģ�K�������l�T��̖(h��o)Tk�͕r(sh��)�g������̖(h��o)Tcr�������£�ݔ�����y(c��)��̖(h��o)���ں���λ�(sh��)��(j��);�y(c��)����(sh��)��(j��)��ȡģ�K���b����̖(h��o)JXc��Ӌ(j��)��(sh��)��ȡ��̖(h��o)Lad�������£�����ݔ��ʹ����̖(h��o)EN�͔�(sh��)��(j��)�����̖(h��o)Dsel�����·քeݔ�����ں���λ�(sh��)��(j��)����MCU�\(y��n)��̎���@ʾ��

����FP

���P(gu��n)��x:

- ...2015/09/24 18:00��FPGA�Դ��(ji��n)��

- ...2012/10/29 10:29�����ϸ����܃x����FPGA,��(sh��)�F(xi��n)�^��WLAN�y(c��)��

- ...2012/10/22 13:14���˽�LabVIEW FPGA��ܛ���O(sh��)Ӌ(j��)���l�x���ă�(y��u)��(sh��)����

- ...2012/09/24 13:59��NI PXI�Y(ji��)��FPGA��(sh��)�F(xi��n)�^��WLAN�y(c��)����֧��802.11ac

- ...2012/09/17 14:04���˽�LabVIEW FPGA��ܛ���O(sh��)Ӌ(j��)���l�x���ă�(y��u)��(sh��)����

- ...2012/08/13 13:22��ʹ��LabVIEW��FPGA�턓(chu��ng)��һ��(g��)�Ԅ�(d��ng)�����������y(c��)ԇϵ�y(t��ng)

- ...���D��Ԕ����܇�x���屳���܇Ҏ(gu��)��(j��)��ȫ�O(sh��)Ӌ(j��)Ҫ��

- ...��ʹ���а�ȫ���ϵ��W��惦(ch��)��(g��u)����ȫ����܇ϵ�y(t��ng)

- ...������ƫ�ò�־��Ԃ��������^���M(j��n)չ�͑�(y��ng)��

- ...�����¿�˹�y(c��)�u(p��ng)ijƷ�����ܲ����������C(j��)����ƪ

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�(�m(x��))

- ...���������ʽ�ضșz�y(c��)���y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...��RTD�y(c��)��ϵ�y(t��ng)�Є�(l��)�����ʧ���Ӱ�

- ...���{(l��n)��BR/EDR �� Bluetooth Smart��ʮ����Ҫ�^(q��)�e

- ...��IoT�W(w��ng)�P(gu��n)ƽ�_(t��i)�c��(y��ng)��

- ...������(qi��ng)��ARM DesignStart��ͨ���ƻ�SoC���^�졢�^���L(f��ng)�U(xi��n)֮·

- ...����(sh��)�w�����D(zhu��n)��O2O���}��(ch��)���������ܻ�ˮƽ�ĺ�������

- ...���N܇��LED�(q��)��(d��ng)�����ı��^

- ...���{(l��n)���䌦(du��)�ڶ�ƪ��������ɷ���

- ...��������A�Ƴ��I(l��ng)�ȵğo����(sh��)��(j��)�ɼ���Q����

- ...����ɭ���댧(d��o)�w����Ј�(ch��ng)څ��(sh��)�ğo����늷���

- ...����ɭ���댧(d��o)�w�����܇�����O(sh��)Ӌ(j��)څ��(sh��)�Ľ�Q����

- ...�� ��о��(chu��ng)�����ø�Уδ����܇�˙C(j��)�����O(sh��)Ӌ(j��)��ِ��(b��o)����ʽ����(d��ng)

- ...�� ̽�صڶ����l(w��i)�{(l��n)ɽ������(chu��ng)�¡�������ԇ�(y��n)���g(sh��)Փ����

- ...�� ��2018�Ї�(gu��)�댧(d��o)�w���B(t��i)朴��(hu��)���ڽ��Kʡ�����e��

- ...�� �����}��Ҏ(gu��)����CITE 2019�t���ǻ�δ��

- ...�� ����܇�����S��TI���ײ������������ڄ�(chu��ng)������ܵ�����

- ...�� �ⷨ�댧(d��o)�w��ST����Cinemo��Valens��CES 2018չ��(li��n)����ʾ��܇��Ϣ�ʘ���Q����

- ...�� ���������·�a(ch��n)�I(y��)��(chu��ng)�°l(f��)չ�߷�Փ�������ھ����_

- ...�� ����늙C(j��)��(qi��ng)��(sh��)����PCIM����2017չ

- ...�� GPGPU��(gu��)�a(ch��n)������Ї�(gu��)оƬ�a(ch��n)�I(y��)�Ŀհ؎�

- ...�� ��(li��n)�W(w��ng)�a(ch��n)Ʒ�O(sh��)Ӌ(j��)��Wi-Fi�B�ӵ��Ă�(g��)�P(gu��n)�I����

- ...�� �������Ї�(gu��)MEMS���܂������a(ch��n)�I(y��)�l(f��)չ���(hu��)�����ڰ������_�Ļ

- ...�� IAIC���(xi��ng)ِ���[���Ї�(gu��)о����(y��ng)�Ä�(chu��ng)�£���Ϣ��ȫ�߷�Փ����������

- ...�� ���ܿ�����Դ�Qλ����

- ...�� ���x5G���ײ�OTA �y(c��)ԇ���g(sh��)

- ...�� ����(g��)�Ј�(ch��ng)�������L(zh��ng)�Ƅ�(d��ng)Molex�ӏ�(qi��ng)��܇�I(l��ng)��İl(f��)չ

- ...�� �Ї�(gu��)�Gɫ����(li��n)�˳������(hu��)���_�ڼ� ���a(ch��n)�W(xu��)���ù�̽�Gɫ�l(f��)չ��ģʽ

- ...�� Efinix® ȫ���(q��)��(d��ng)AI߅��Ӌ(j��)�㣬�ɹ��Ƴ�Trion™ T20 FPGA��Ʒ, ͬ�r(sh��)���a(ch��n)Ʒ�U(ku��)չ����ʮ�f߉��Ԫ��T200 FPGA

- ...�� Ӣ�w�������M(j��n)����(hu��)�����I(l��ng)�ǻ�������

- ...�� ��늮a(ch��n)Ʒ�_�l(f��)���y(c��)ԇ��ӑ��(hu��)��������Դ����(ch��ng)�ɹ��e��

- ...�� Manz���ǿƼ�����댧(d��o)�w�I(l��ng)�� ����弉(j��)�ȳ��ͷ��b�ṩ���W(xu��)���Ƴ̡�Ϳ�������⑪(y��ng)�õ����a(ch��n)�O(sh��)���Q����

- ...�� ������ABITRODE��(d��ng)��늳y(c��)ԇϵ�y(t��ng)���������������Դ

- ...�� ������AFTFϵ��늳y(c��)ԇϵ�y(t��ng)�И�(bi��o)��������Դ��܇�ɷ�����˾

- ...�� ������A���ʸ߉���Դ����ʽؓ(f��)�dϵ�y(t��ng)�ɹ����������؈

- ...�� ������A��(gu��)�H��늄�(d��ng)��܇���P(gu��n)�I�����y(c��)�u(p��ng)��ӑ��(hu��)�����[���M(j��n)�y(c��)�u(p��ng)���g(sh��)

- ...�� ��(sh��)��(j��)�ɼ��K��ϵ�y(t��ng)�O(sh��)��

- ...�� ��(ji��n)�x�Ƽ�̤��������

- ...�� ���`˼® ���� AEC-Q100 �Y�|(zh��)�J(r��n)�C����܇ϵ�Юa(ch��n)ƷӋ(j��)��

- ...�� ���`˼® �����U(ku��)������� ⁽�ϵ��™ FPGA �a(ch��n)Ʒ ⁽�ϵ�Юa(ch��n)Ʒ�U(ku��)�������� 1M ߉��Ԫ�� FPGA

- ...�� ���`˼® ����Trion® Titanium ���_(t��i)�e� (TSMC) 16�{��ˇ��(ji��)�c(di��n)��Ƭ

- ...�� TI��2019��ȫ��(gu��)��W(xu��)������O(sh��)Ӌ(j��)��(j��ng)ِ�C��(ji��ng)��Y�ھ��e��

- ...�� BlackBerry QNX̓�M�C(j��)�@��ȫ���ׂ�(g��)��܇��ȫ�����Եȼ�(j��)(ASIL) ��D���J(r��n)�C

- ...�� ���R��܇�x��BlackBerry������һ����܇